- 产品描述

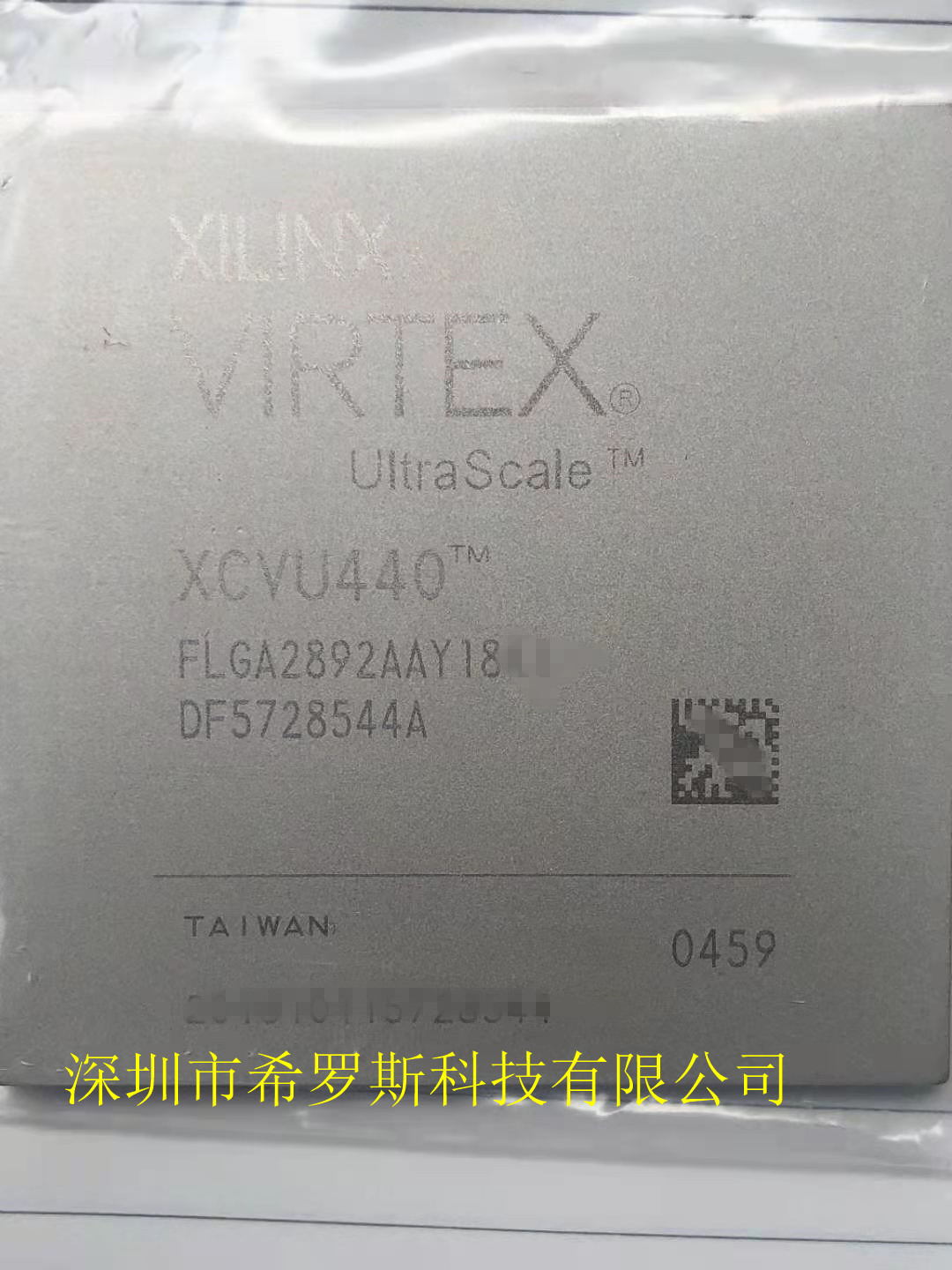

深圳市希罗斯科技有限公司是一家主营Xilinx/Broadcom/Altera/AD/TI的分销商, 为国内研究所机构及高等院校提供一站式服务平台。型号齐全,长期供应,信誉度较高。我们能提供的产品广泛,应用于航空航天、船舶、汽车电子、计算机、铁路、电子、通信网络、电力工业以及大型工业设备等。深圳市希罗斯科技有限公司坚守以客户,质量,信誉的原则,层层把关渠道,把控质量,每片产品来源可追溯,得到了广大客户的认可和支持。深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 通信 微波 雷达导弹 战舰 航海等重型设备和**&高可靠设备。希罗斯科技专注**IC数十年,只做原装**!

产品定位:工业级及以上电子元器件。

优势产品系列:Artix-7/Kintex-7/Spartan-6/Kintex UltraScale/Virtex UltraScale/Virtex-7/ZYNQ Ultrascale/Zynq-700/*级XQ系列/ 开发板及套件。

Virtex-5系列

Virtex®-5 FPGA 是世界上 65nm FPGA 系列,采用 1.0v、三栅较氧化层工艺技术制造而成,并且根据所选器件可以提供 330,000 个逻辑单元、1,200 个 I/O 引脚、48 个低功耗收发器以及内置式PowerPC™440、PCIe® 端点和以太网 MAC 模块。已经提供了5种系列平台,分别是LX、LXT 、SXT、FXT、TXT,每种平台高性能逻辑、串行连接功能、信号处理和嵌入式处理性能方面实现了佳平衡。例如LX针对高性能逻辑进行了优化,LXT针对具有低功耗串行连接功能的高性能逻辑进行了优化,SXT针对具有低功耗串行连接功能的DSP 和存储器密集型应用进行了优化。Virtex-5 FXT 则用于实现具有速率高的串行连接功能的嵌入式处理,Virtex-5 TXT可用于实现**高带宽应用,如有线通信与数据通信系统内的桥接、开关和集聚。

Virtex-6 FPGA系列

基于采用*三代Xilinx ASMBL™ 架构的40nm制造工艺,Virtex-6 FPGA系列还拥有新一发工具和早已针对Virtex-5 FPGA而开发的广泛IP库支持。这些都为多产的开发和设计移植提供了强大的支持。 与竞争厂商提供的40nm FPGA产品相比,新的Virtex-6 FPGA系列器件性能提高15%,功耗降低15%。新器件在1.0v内核电压上操作,同时还有可选的0.9v低功耗版本。 这些使得系统设计师可在设计中采用Virtex-6 FPGA,从而支持建设“绿色”中心办公室和数据中心。对于电信行业这一点特别重要,因为该行业正在扩展对因特网视频和富媒体内容的支持。

Virtex- 6 FPGA系列包括三个面向应用领域而优化的FPGA平台,分别提供了不同的特性和功能组合来较好地满足不同客户应用的需求:

Virtex-6 LXT FPGA—优化目标应用需要高性能逻辑、DSP以及基于低功耗GTX 6.5Gbps串行收发器的串行连接能力。

Virtex-6 SXT FPGA—优化目标应用需要**高性能DSP以及基于低功耗GTX 6.5Gbps串行收发器的串行连接能力。

Virtex-6 HXT FPGA—作为优化的通信应用需要高的串行连接能力,多达64个GTH串行收发器可提供高达11.2Gbps带宽 。

Virtex-6 FPGA把的硬件芯片技术、创新的电路设计技术以及架构上的增强结合在一起,与**代Virtex器件以及竞争FPGA产品相比,功耗大大降低,性能较高并且成本较低。表3-15显示了Virtex-6FPGA系列主要技术特征。

VCU128 评估套件现已推出量产 Virtex UltraScale + HBM FPGA。VCU128 评估套件集成了全新的赛灵思 Virtex UltraSacle+ VU37P HBM FPGA,可在 FPGA 裸片旁边集成 8GB HBM DRAM,从而实现大容量存储器带宽以及较小的 PCB 封装尺寸。

Virtex UltraScale+ HBM FPGA 可以很大程度缓解高性能计算、数据库以及网络加速应用中使用并行存储器(比如DDR4)所带来的带宽和功耗瓶颈。

VCU128 评估套件针对使用 Virtex UltraScale+ HBM FPGA 的快速原型设计进行了优化。使用 VCU128 的大容量存储器带宽和高速 I/O 连接,开启您的设计吧。

Virtex®-5 FPGA采用了新的65工艺,结合低功耗IP块将动态功耗降低了35%;此外,还利用65nm三栅较氧化层技术保持低静态功耗; 利用65nm ExpressFabric技术,实现了真正的6输入LUT,并将性能提高了2个速度级别。内置有用于构建较大型阵列的FIFO逻辑和ECC的增强型36 Kbit Block RAM带有低功耗电路,可以关闭未使用的存储器。 逻辑单元多达330,000个,可以实现**的高性能; I/O引脚多达1,200个,可以实现高带宽存储器/网络接口,1.25 Gbps LVDS; 低功耗收发器多达24个,可以实现100 Mbps - 3.75 Gbps高速串行接口; 核电压为1V,550 MHz系统时钟; 550 MHz DSP48E slice内置有25 x 18 MAC,提供352 GMACS的性能,能够在将资源使用率降低50%的情况下,实现单精度浮点运算; 利用内置式PCIe端点和以太网MAC模块提高面积效率 ; 较加灵活的时钟管理管道(Clock Management Tile)结合了用于进行时钟相位控制与抖动滤除的新型PLL和用于各种时钟综合的数字时钟管理器(DCM); 采用了*二代sparse 封装,改善了信号完整性,并降低了系统成本; 增强了器件配置,支持商用flash存储器,从而降低了成本。

注:一个Virtex-5 Slice具有4个LUT和4个触发器,而一个前文所提及的常规Slice只包含2个LUT个2个触发器。每个DSP48E包含一个25*18位的硬核乘法器、一个加法器和一个累加器。

欢迎来到深圳市希罗斯科技有限公司网站,我公司位于经济发达,交通发达,人口密集的中国经济中心城市—深圳。 具体地址是广东深圳公司街道地址,负责人是刘小姐。

主要经营集成电路。

我们公司主要供应集成电路等产品,我们的产品货真价实,性能可靠,欢迎电话咨询!

本页链接:http://www.cg160.cn/vgy-73906600.html

以上信息由企业自行发布,该企业负责信息内容的完整性、真实性、准确性和合法性。阿德采购网对此不承担任何责任。 马上查看收录情况: 百度 360搜索 搜狗

关于深圳市希罗斯科技有限公司

商铺首页 |

更多产品 |

联系方式

深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 ..

- 我要给“XC3S200-4VQG100I 海外渠道”留言

- 更多产品