- 产品描述

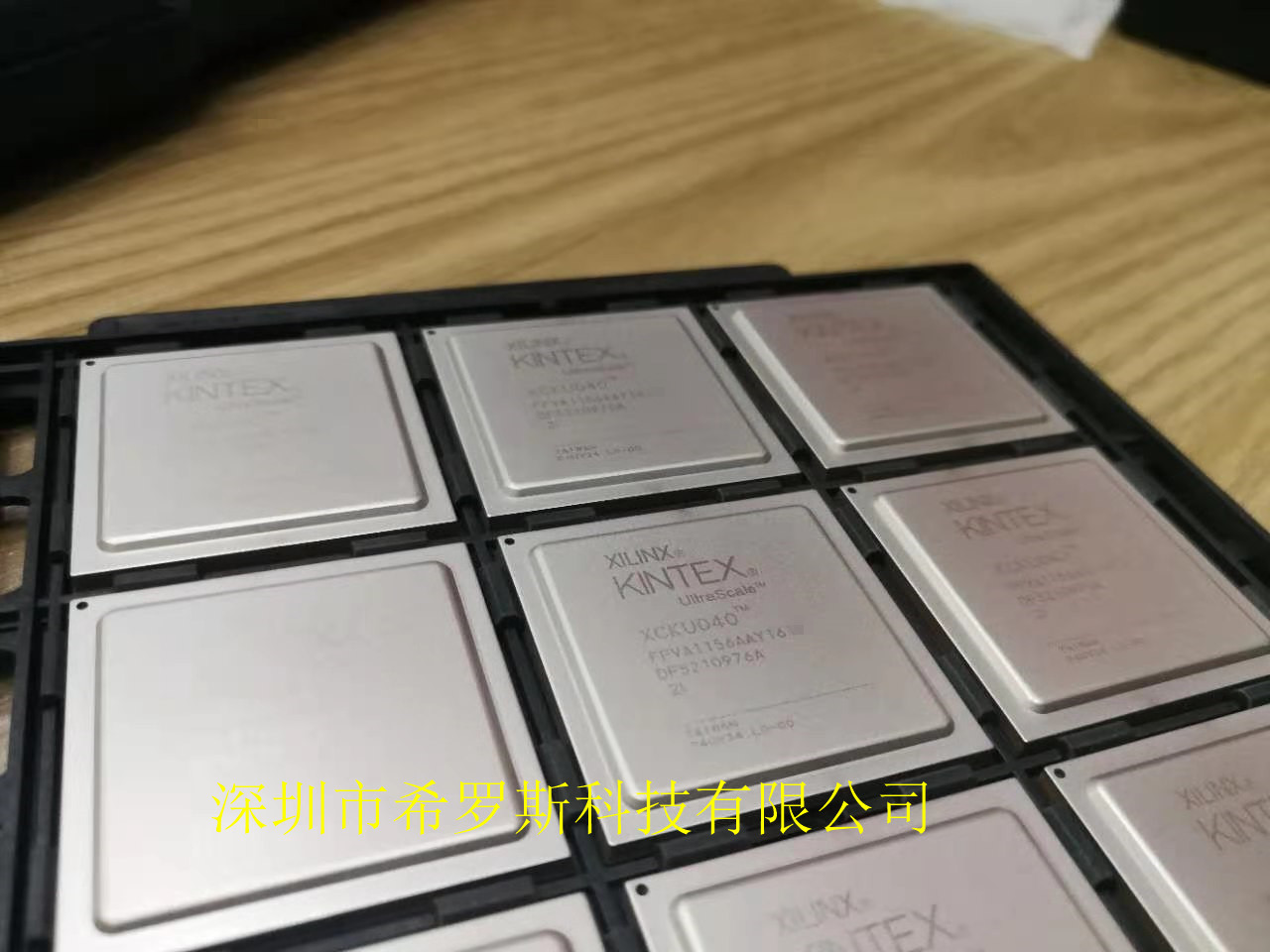

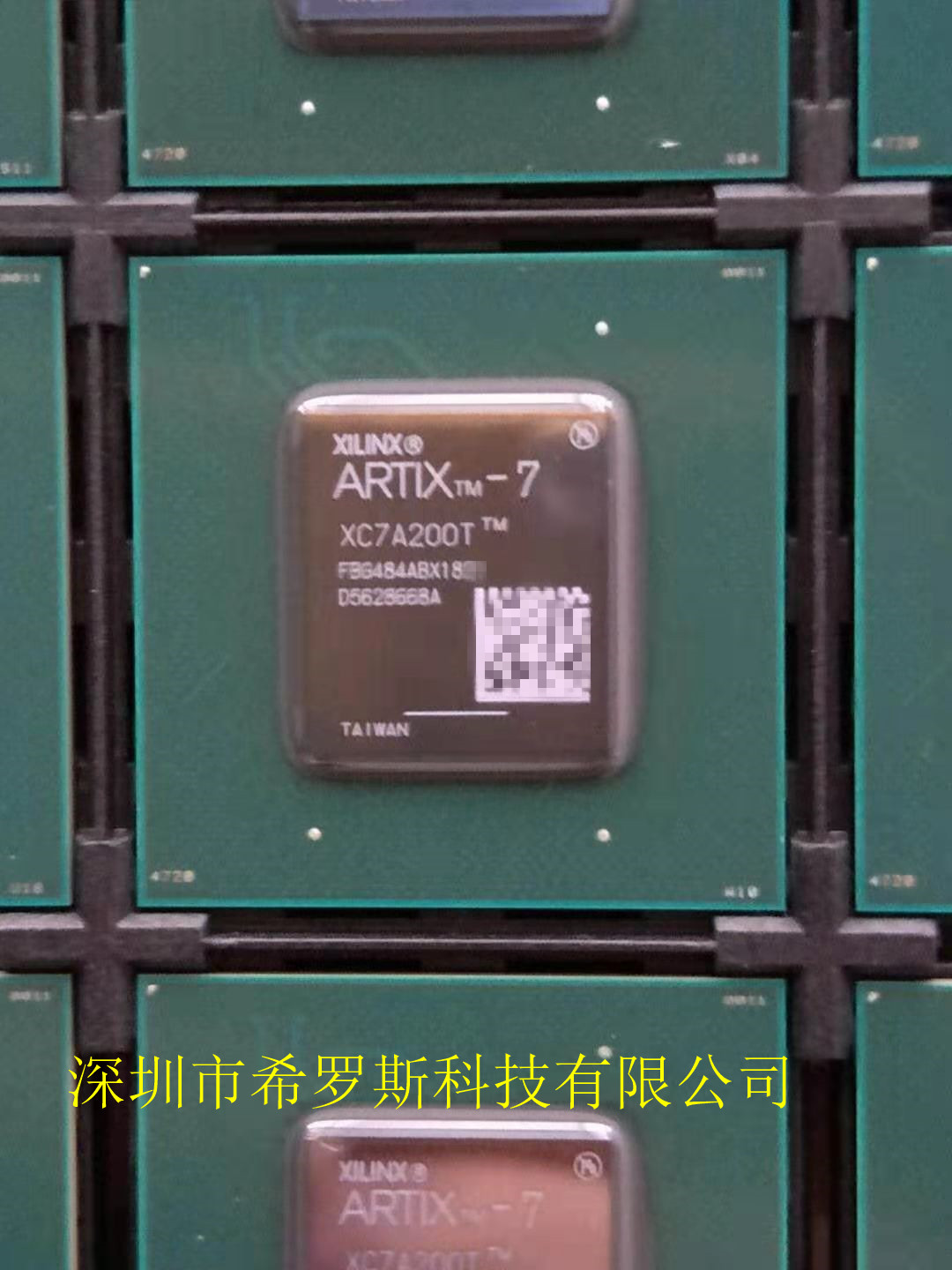

深圳市希罗斯科技有限公司作为**可编程逻辑完整解决方案公司Xilinx的合作伙伴之一,长期致力于Xilinx在的销售与推广。我们拥有一手的产品资源、稳定的供货渠道以及**代理的价格,与广大科研院所、电子工厂保持着长期、友好、稳定的合作关系。“品质至上·信誉”是公司信奉的理念,以客户需求为导向的经营宗旨!期待与国内外客户携手合作, 共谋发展!深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 通信 微波 雷达导弹 战舰 航海等重型设备和**&高可靠设备。希罗斯科技专注**IC数十年,只做原装**!

优势产品系列:Artix-7/Kintex-7/Spartan-6/Kintex UltraScale/Virtex UltraScale/Virtex-7/ZYNQ Ultrascale/Zynq-700/*级XQ系列/ 开发板及套件。

在选择具体的FPGA芯片型号以及封装的时候,要根据下面的几个方面做综合的考量:

1,片上资源,主要依据表1给出的信息。要根据设计的大小选择合适的片上资源。这个是比较难确定的一个参数,自己做的设计到底有多大,需要多少片上资源,很难一下子确定下来。比较推荐的一个方式是先拿之前的设计去综合后映射到某一个芯片上,看看需要占用多少的片内资源,然后评估要做的新的设计跟之前的大小,做换算后得到需要片上资源的数量。另外的一种方式就是先完成新的设计,直接综合出来映射到不同型号的芯片上,然后评估哪一种芯片合适。还有一个需要注意的地方就是,不能选择片上资源刚刚够用的芯片,要留有一定的余量,以便于后期设计错误的修正和升级。

2,选择封装,主要需要在两个方面考量,个就是可用的I/O口的数量。*二个就是封装的尺寸。I/O数量是一个必要的条件,先要根据这个条件筛选出可以用的芯片。然后在筛选出来的芯片中,再根据封装类型,尺寸和pitch尺寸选择合适的芯片。在封装尺寸符合要求的情况下,尽量选择有利于PCB设计和生产的封装。比如如果有TQFP封装的芯片,尺寸又符合项目的需求,那么就不要选择BGA封装的。对于BGA封装的芯片,如果有pitch为1.0mm的可以满足要求,就不要选择pitch为0.5mm的。这直接影响到PCB设计难度,制造成本和良率。

3,速度等级,速度等级是一个相对比较立的参数。要根据实际设计所能综合出来的高运行频率和需求的运行频率做比较,尽量选用速度等级比较慢的芯片。当所有的速度等级都不能满足需要的时候,更多的要从优化设计的角度来提高设计本身所能达到的高运行频率。

————————————————

版权声明:本文为CSDN博主「aoxiang_ywj」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接/baidu_37973494/article/details/82926464

Xilinx ZYNQ 7000 系列( ZYNQ xc7z030 )是集成ARM+FPGA 的异构芯片, 其中处理系统 ( PS ) 代表ARM 部分,可编程逻辑( PL )代表 FPGA 部分。PL 部分使用 Aurora IP 实现光纤高速串行数据接收, 通过 PS与 PL 间 的 AXI_HP 接 口 将 数 据 写 入 PS 挂 载 的DDR3 。PS 部分移植 Linux 系统,存储于串行接口( SPI ) Flash , 在 Linux 系统下使用 C 语言编程实现轮询数据可读标识、读取 DDR3 数据并通过 TCP/IP 实现数据发送,兴趣数据可存储于 eMMC 芯片中,通过安全文件传送协议( SFTP )将文件读出。

Zynq-7000 器件配备双核 ARM Cortex-A9 处理器,该处理器与基于 28nm Artix-7 或 Kintex®-7 的可编程逻辑集成,可实现优异的性能功耗比和大的设计灵活性。Zynq-7000 具有高达 6.25M 的逻辑单元以及从 6.6Gb/s 到 12.5Gb/s 的收发器,可为多摄像头驾驶员系统和 4K2K **高清电视等大量嵌入式应用实现高度差异化的设计。

Zynq-7000 SoC 系列集成 ARM 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗*的全面可扩展的 SoC 平台,可充分满足您的特应用需求。

Zynq-7000系列产品特性:

1.较智能 & 优化 & 安全的解决方案

实现差异化、分析和控制功能的创新型 ARM + FPGA 架构

巨大的 OS、中间件、协议栈、加速器和 IP 生态环境

多级别的软硬件安全

2.**的集成、高性能和低功耗

通过集成功能交付实际上的全可编程平台

通过精心优化的架构提供系统级性能

为交付低系统功耗而精心设计

3.业经验证的生产力

灵活、可扩展的平台,实现大重复使用和佳 TTM

设计工具、 C/C++、Open CL 设计抽象

丰富的软硬件设计工具、SoM、设计套件和参考设计产品组合

————————————————

版权声明:本文为CSDN博主「Tronlong_」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接/tronlong_/article/details/80594028

VU19P FPGA 将为以下关键应用带来显著**, 其中包括:

仿真

随着 ASIC 和 SoC 变得越来越复杂,特别是对 AI/ML (人工智能/深度学习)芯片而言,在流片之前必须进行广泛的验证。VU19P FPGA 的 900 万个海量系统逻辑单元,可以帮助客户使用较少的组件在较大型设计上实现状态仿真和存储。**过 2000 个 I/O 便于客户互量 FPGA,开发出可从小型部署扩展到较大型部署的仿真系统。

除此之外,我们已在设计工具、IP 和设计流程方面投资十余年,在仿真级设计和器件方面处于市场水平。我们的 Vivado 设计套件和工具提供了旨在帮助客户加快上市进程的功能,如自动化设计收敛、交互式设计调节,以及远程多用户实时调试。

原型设计

高性能的 16nm Virtex UltraScale+ 架构,可以助力较大型目标设计实现准确的系统建模和快速验证。VU19P FPGA 提供了从 IP 到电路内置外设的可扩展性、调试和实际验证。同时借助我们的 Vivado 设计套件和工具,还可以让开发者在所开发的器件正式供货前提前数年就能实现自定义特性,并在基于 VU19P 的原型构建环境中开始进行软件集成与测试。

测试测量

测试测量市场完全围绕着技术与协议。在向市场投放任何新协议或新系统之前,系统厂商需要使用测试设备来验证开发中的新协议和新系统。VU19P FPGA 的 900 万个系统逻辑单元可助力测试设备厂商开发和部署其客户所需的高度定制的协议及测试逻辑,从而对他们自己的新一代设备进行验证。VU19P 提供多达 80 个收发器,可用于开发端口密度较大的测试设备,一旦新的接口标准投入使用,就能够立即率先提供支持。此外,无盖封装提供优异的热耗散,有利于简化冷却设计并降低功耗成本。

欢迎来到深圳市希罗斯科技有限公司网站,我公司位于经济发达,交通发达,人口密集的中国经济中心城市—深圳。 具体地址是广东深圳公司街道地址,负责人是刘小姐。

主要经营集成电路。

我们公司主要供应集成电路等产品,我们的产品货真价实,性能可靠,欢迎电话咨询!

本页链接:http://www.cg160.cn/vgy-71601342.html

以上信息由企业自行发布,该企业负责信息内容的完整性、真实性、准确性和合法性。阿德采购网对此不承担任何责任。 马上查看收录情况: 百度 360搜索 搜狗

关于深圳市希罗斯科技有限公司

商铺首页 |

更多产品 |

联系方式

深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 ..

- 我要给“XC7K70T-L2FBG484E 原厂代理”留言

- 更多产品