- 产品描述

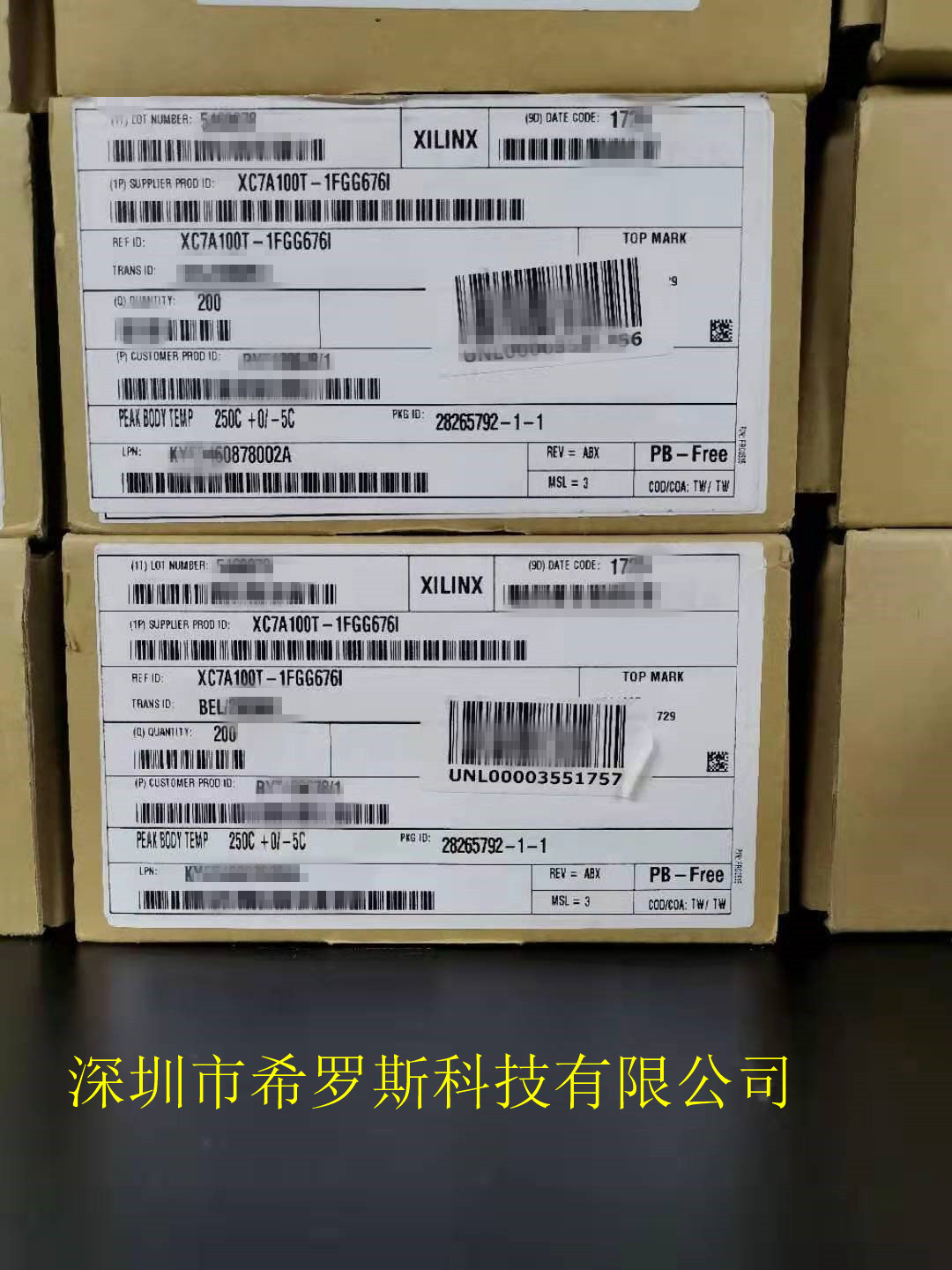

深圳市希罗斯科技有限公司作为**可编程逻辑完整解决方案公司Xilinx的合作伙伴之一,长期致力于Xilinx在的销售与推广。我们拥有一手的产品资源、稳定的供货渠道以及**代理的价格,与广大科研院所、电子工厂保持着长期、友好、稳定的合作关系。“品质至上·信誉”是公司信奉的理念,以客户需求为导向的经营宗旨!期待与国内外客户携手合作, 共谋发展!深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 通信 微波 雷达导弹 战舰 航海等重型设备和**&高可靠设备。希罗斯科技专注**IC数十年,只做原装**!

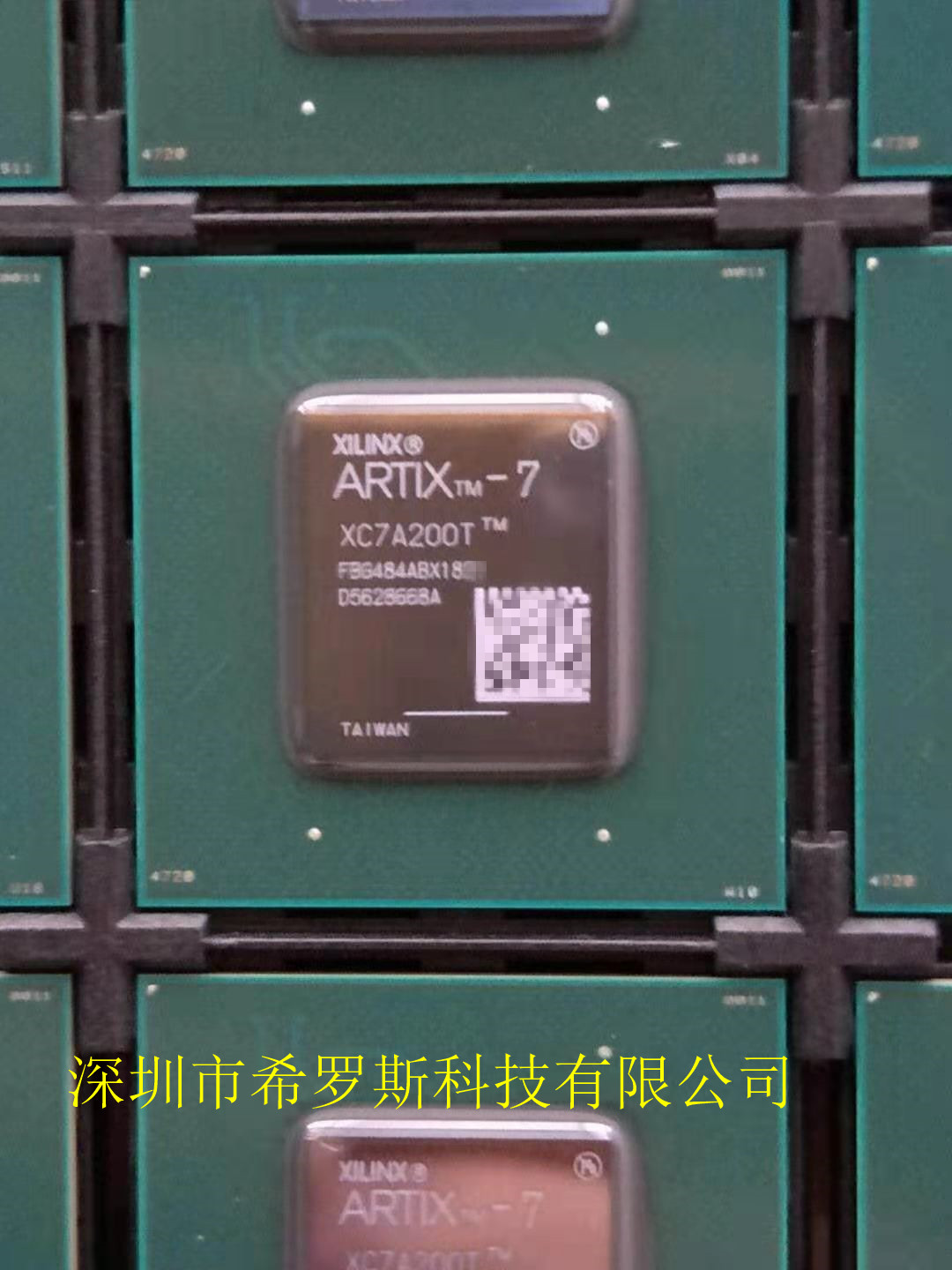

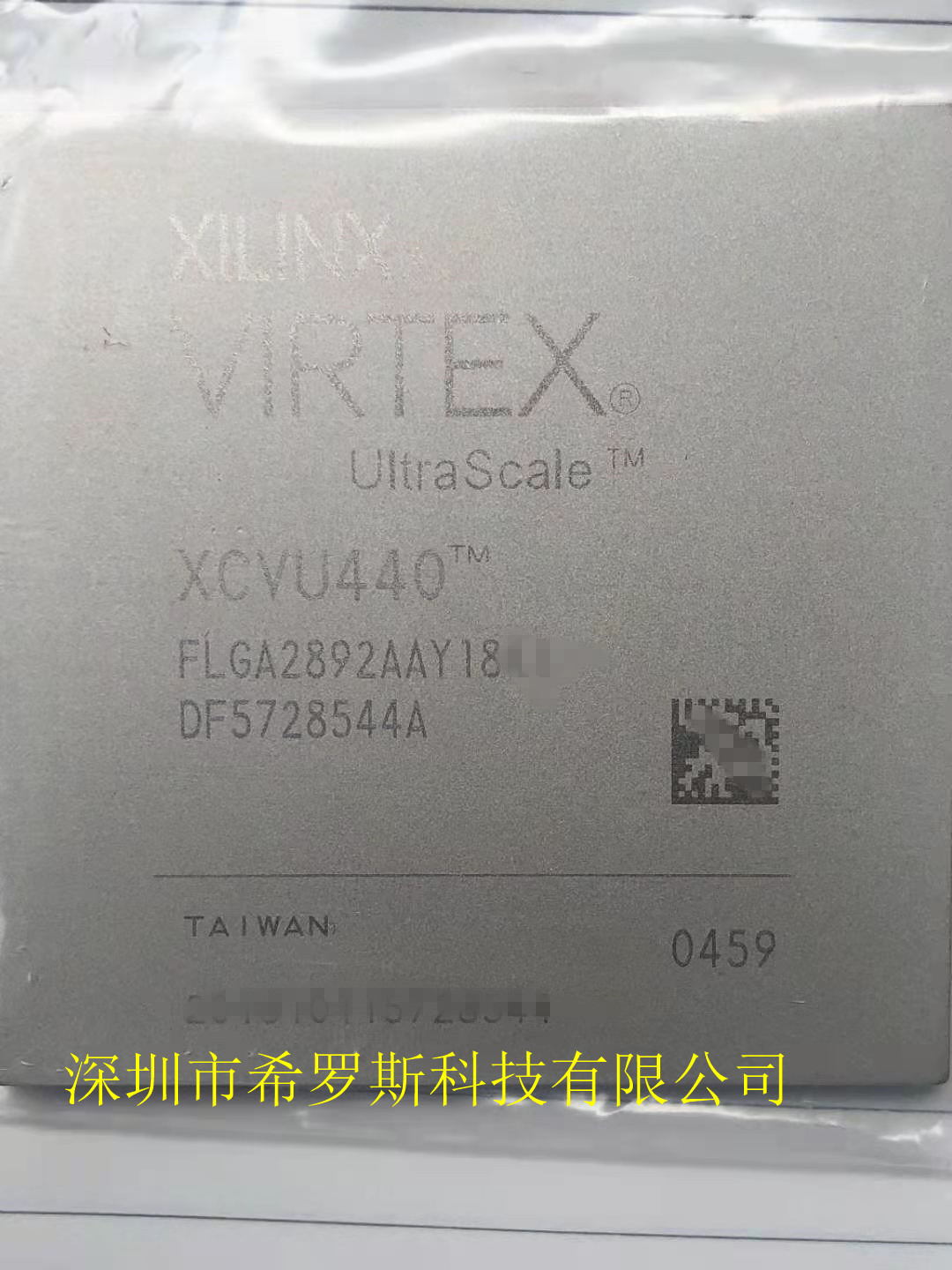

优势产品系列:Artix-7/Kintex-7/Spartan-6/Kintex UltraScale/Virtex UltraScale/Virtex-7/ZYNQ Ultrascale/Zynq-700/*级XQ系列/ 开发板及套件。

Virtex UltraScale+ HBM FPGA 的特别之处在于整合 AXI 埠交换器,可从任意 AXI 端口存取任意的内存位置,节省 25 万个查找表、37 万个正反器和**过 4W 的功耗。该交换器不但能够缩小设计尺寸、简化设计,而且还有助于达成时序收敛、加快产品的上市速度并降低营运成本(OPEX)。

此外,此款新组件还整合了高速连接,如采用 RS-FEC 模块的 100G 以太网络、150G Interlaken、PCIe Gen4 等,协助简化设计工作并加快上市速度。

适用赛灵思新款组件的应用包括:

● 运算加速:对数据进行预处理是实现佳效能的关键。Virtex UltraScale+ VU57P 不同于具备固定功能的操作数件,它拥有可自行调适的逻辑和 460GB/s 的 HBM 带宽,能够选择、转换和整理数据,从而为目标加速器进行输入优化。使用其高速 PAM4 收发器,赛灵思新款 FPGA 可大化传输量和系统效能。

● 新一代*墙:网络营运商需要不间断且强大的网络可用性,在**数据安全并防止恶意软件攻击企业网络的前提下实现智能管理。Virtex UltraScale+ VU57P FPGA 凭借线路速率下数以万计的并行会话(session),为实现多层网络安全提供优异的可扩展性。透过 16GB HBM,安全应用在缓冲和重新排序网络流的同时能够管理多个查找表。58G PAM4 收发器支持新的光通讯标准,可实现新一代*墙所需的较高传输量。

● 具备 QoS 功能的交换器和路由器:配 备16GB HBM 的 Virtex UltraScale+ VU57P FPGA 可透过用于 QoS 功能的 400G 数据路径工作流程和流量管理员提供 Nx400G / 200G / 100G / 50G 交换。58G PAM4 收发器能够使用新的光通讯标准建立连接,将外部组件的传输率提高一倍。查找表和流量管理员队列则在 HBM DRAM 内执行。因为设计中充分考虑了功耗和散热的需求,基于 Virtex UltraScale+ VU57P FPGA 的交换器和路由器能够选择无盖封装,以较简单的散热方式达到较能,这对于数据中心和电信基础设施具有重要意义。

赛灵思宣布 Virtex UltraScale+ 系列产品再添的高速运算新成员 — Virtex UltraScale+ VU57P FPGA。这是一款新型高带宽内存(HBM)组件,能够在较快速度、低延迟和较低功耗需求下传输大量数据。新型 Virtex UltraScale+ VU57P FPGA 融合了一系列强大的功能,适用于数据中心及有线与无线通信中要求严苛的众多应用。

与DDR4等分离式标准型内存(discrete commodity memories)相比,赛灵思 Virtex UltraScale+ VU57P FPGA 的内存带宽和容量大幅提高,是延迟敏感型工作负载的**选择,而在这些工作负载中,高速的数据传输量和快速内存是关键需求。它整合低功耗运算力与高达 460GB/s 的较高内存带宽和容量,同时采用的 PAM4 高速收发器,与主流 25G 收发器相比可实现两倍的传输速率。整合的 HBM 控制器和 AXI 埠交换器可提供对整个 16GB HBM 内存连续存取。

Virtex UltraScale+ HBM FPGA 的特别之处在于整合 AXI 埠交换器,可从任意 AXI 端口存取任意的内存位置,节省 25 万个查找表、37 万个正反器和**过 4W 的功耗。该交换器不但能够缩小设计尺寸、简化设计,而且还有助于达成时序收敛、加快产品的上市速度并降低营运成本(OPEX)。

此外,此款新组件还整合了高速连接,如采用 RS-FEC 模块的 100G 以太网络、150G Interlaken、PCIe Gen4 等,协助简化设计工作并加快上市速度。

基于 Xilinx Zynq-7000 SoC 系列架构,广州创龙设计了一款适用于高速数据采集处理的**板SOM-TLZ7x ,采用沉金无铅

工艺的 12 层板设计。

1.**板简介:

基于 Xilinx Zynq-7000 SoC 高性能低功耗处理器,集成 PS 端单核/双核 Cortex-A9 ARM+ PL 端 Artix-7 架构可编程逻辑资源;

PS 端高主频可达 866MHz;

支持 USB 2.0、SDIO、千兆网等多种高速接口,同时支持 I2C、SPI 等常见接口;

支持两路 12bit MSPS ADC,多达 17 个差分输入通道;

多达 54 个复用 I/O 引脚,用于外设引脚分配;

PS 端可通过 EMIO 配置 PL 端 IO,支持共享内存,支持 PS 端和 PL 端数据协同处理;

PL 端可编程逻辑单元数量区间为 23K-85K,内部集成的 Block RAM 可达 4.9MByte;

可通过 PS 端配置及烧写 PL 端程序,且 PS 端和 PL 端可以立开发,互不干扰;

**板体积极小,大小仅 62mm*38mm;

连接稳定可靠,采用工业级精密 B2B 常规连接器,保证信号完整性;

提供 PL 端与 PS 端的片内通信开发教程。

————————————————

版权声明:本文为CSDN博主「Tronlong_」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接/tronlong_/article/details/80594028

回到产品规格比较,UltraScale+VU19P与Stratix 10 GX 10M间的主要差异,在于制程采用上有所不同,前者的逻辑闸数量为900万个(实际为8,938K),后者则为1,020万个,只不过后者的做法显然是采用系统级封装方式,将两款Stratix 10 GX FPGA产品(逻辑闸数量为510万个),以EMIB封装加以整合。

就Xilinx描述来看,并未见到相当鲜明的封装技术搭配,若以单一裸晶角度来看,Xilinx逻辑闸数量应该是业界高的FPGA,但以完成封装后的芯片方案而言,则是英特尔的Stratix 10 GX 10M略胜一筹。此外,Stratix 10 GX 10M已经进入量产时程,就时间点来看抢先Xilinx一步,这对Xilinx来说,即便在单一裸晶数量比较上胜出,但未能抢下市场,或许**会沦为叫好而不叫座的情况。

欢迎来到深圳市希罗斯科技有限公司网站,我公司位于经济发达,交通发达,人口密集的中国经济中心城市—深圳。 具体地址是广东深圳公司街道地址,负责人是刘小姐。

主要经营集成电路。

我们公司主要供应集成电路等产品,我们的产品货真价实,性能可靠,欢迎电话咨询!

本页链接:http://www.cg160.cn/vgy-70434701.html

以上信息由企业自行发布,该企业负责信息内容的完整性、真实性、准确性和合法性。阿德采购网对此不承担任何责任。 马上查看收录情况: 百度 360搜索 搜狗

关于深圳市希罗斯科技有限公司

商铺首页 |

更多产品 |

联系方式

深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 ..

- 我要给“XC7K420T-1FFG901C 正规报关渠道”留言

- 更多产品