- 产品描述

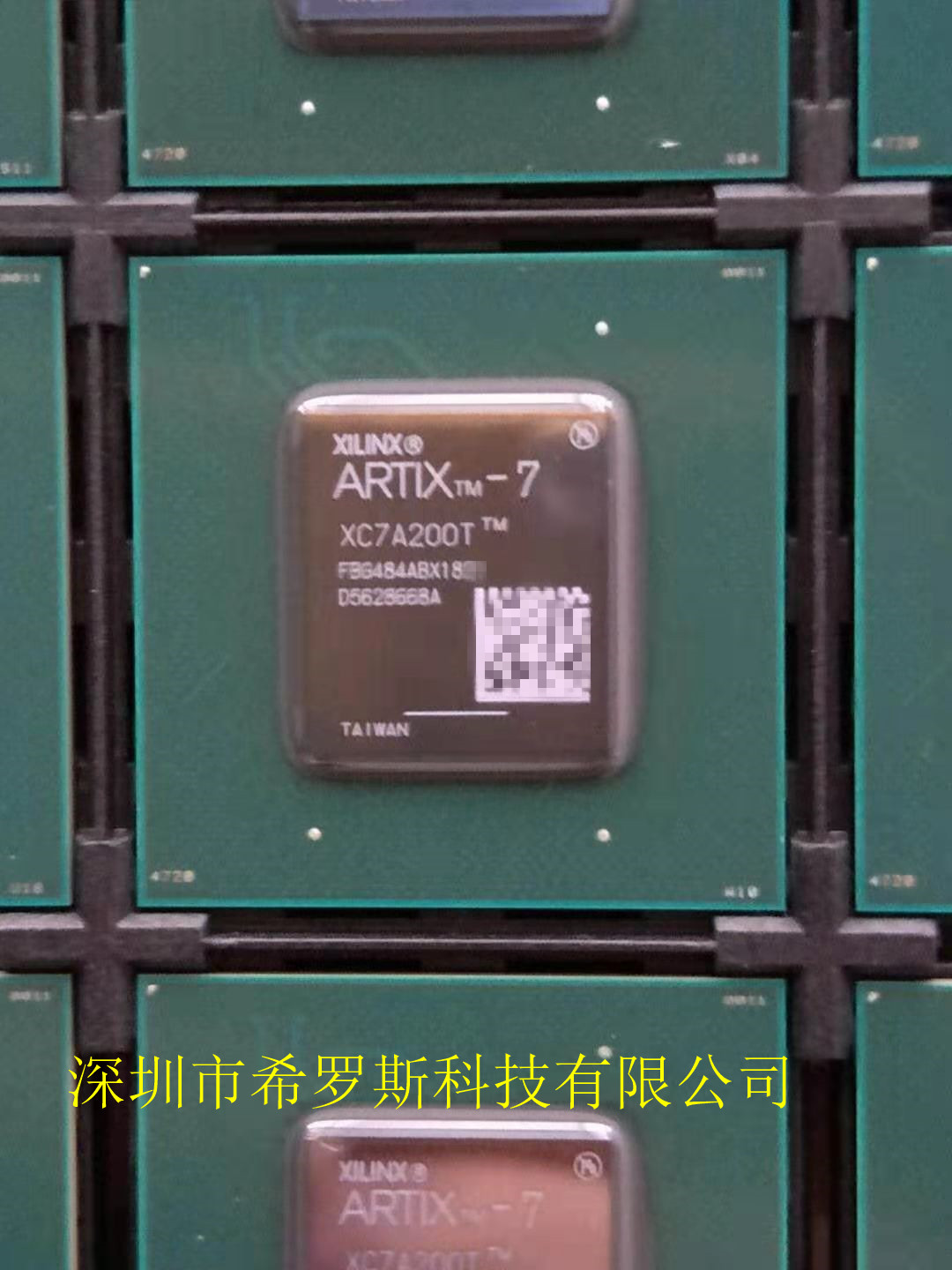

深圳市希罗斯科技有限公司是一家主营Xilinx/Broadcom/Altera/AD/TI的分销商, 为国内研究所机构及高等院校提供一站式服务平台。型号齐全,长期现货供应,信誉度较高。我们能提供的产品广泛,应用于航空航天、船舶、汽车电子、计算机、铁路、电子、通信网络、电力工业以及大型工业设备等。深圳市希罗斯科技有限公司坚守以客户,质量,信誉的原则,层层把关渠道,把控质量,每片产品来源可追溯,得到了广大客户的认可和支持。深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 通信 微波 雷达导弹 战舰 航海等重型设备和**&高可靠设备。希罗斯科技专注**IC数十年,只做原装**!

产品定位:工业级及以上电子元器件。

优势产品系列:Artix-7/Kintex-7/Spartan-6/Kintex UltraScale/Virtex UltraScale/Virtex-7/ZYNQ Ultrascale/Zynq-700/*级XQ系列/ 开发板及套件。

FlexRIO是美国国家仪器(NI)应用赛灵思FPGA为PXI平台开发的新产品系列,是工业中个将NI LabVIEW FPGA技术和高速仪器级I/O。借助FlexRIO, 可以在FPGA硬件中添加定制的信号处理算法,并通过可互换的适配器模块在LabVIEW FPGA编程环境下与I/O互来创建满足应用要求 (包括采样率、带宽、分辨率和通道数量等)的**硬件,而不需要向以**样开发高成本的自定义硬件。

FlexRIO系列产品的采用了PCIe Gen 3 x8连接,在不需要通过主机芯片传输数据的情况下,模块间能够以几GB/s的速率进行数据传输。多达16条数据流可被同时支持,简化了复杂的多FPGA通信方案而不耗费主机CPU资源。NI通过使用高性能赛灵思 Kintex UltraScale系列 FPGA来设计FlexRIO产品中的高速PXI模拟信号数字转换器和PXI数字信号处理器,能够提供比先前基于Kintex-7系列FPGA的模块更多的可编程资源。Kintex UltraScale系列器件采用20nm工艺,能够提供佳的性能功耗比。整个可编程系统有多达150万个逻辑单元,采用*二代3D IC设计,多芯片集成面向DSP密集型应用。在系统性能、BOM成本削减、总功耗削减以及加速设计生产力等方面都有所提升。

由于使用了高性能的FPGA技术和AD采样技术,数字转换器模块有高分辨率、高速采样率和宽带宽而不失动态范围。例如PXIe-5763可以提供500MS/s的采样率,16的分辨率和每通道将近400MHz的带宽。协处理器模块可以为FlexRIO提供额外的DSP性能,配合其他的PXI仪器,协处理器模块可以提供更多的FPGA资源来实时运行复杂算法。

FlexRIO产品的一个主要特点是有方便的编程环境,用户可以使用友好的LabVIEW FPGA软件模块来自定义FPGA设计。除此之外,也可以使用对于FPGA开发者熟悉的Xilinx Vivado工具的项目导出功能为FlexRIO硬件开发,仿真和编译,以获得较高的性能或满足*特的应用要求。

全局复位并不是好的处理方式

我们习惯上通常使用的复位有三种,

硬件开关:复位信号接一个拨码开关。

电源芯片:上电时候电源芯片产生,可以长时间维持,直到稳定。

控制芯片:控制芯片产生复位脉冲。

这些复位信号和FPGA内部信号的变化比起来是比较慢的。复位按钮快也会到达毫秒级别,而FPGA内部信号都是纳秒级别的变化。全局复位的周期远大于系统时钟的周期,是完全可以保证所有的触发器被成功复位的。

但随着系统的频率越来越快,全局复位信号的释放形成一个高扇出的网络。

Fan-out即扇出,模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。

EK-U1-VCU128-G主要特性与优势:

针对计算密集型应用进行了优化

适用于当前和下一代系统设计的高速连接

关键性能与优势

8GB HBM Gen2 集成封装

高可达 460GB/s HBM 带宽

多个外部存储器接口(RLDRAM3、QDR-IV、DDR4)

适用于 PCIe Gen3 x16,或者 Gen4 x8

提供 4 路 32Gb/s QSFP28 接口

购买与交货

价格: $8,995.00

产品编号:EK-U1-VCU128-G

交货周期:4 周

器件信息

Virtex UltraScale+ HBM FPGA

逻辑单元 (K): 2852

HBM DRAM (GB): 8

DSP: 9024

Block RAM+UltraRAM(Mb): 340.9

GTY 32.75Gb/s 收发器: 96

HP I/O: 624

并不是所有部分的设计都需要复位,所以设计者在设计过程中应该准确判断需要被复位的部分,从而采用异步复位、同步释放的方法进行对复位的严格处理。

当我们在设计每一个部分的时候,都要内心问问自己,这个bit需要被复位吗?

那么怎样处理Xilinx FPGA中的复位呢?Xilinx的也给出了解释和方法。

简单总结就是,Xilinx的FPGA 应该尽量避免全局复位,有些部分的设计都可以不用复位,必需要复位的设计而采用 同步 高复位。

欢迎来到深圳市希罗斯科技有限公司网站,我公司位于经济发达,交通发达,人口密集的中国经济中心城市—深圳。 具体地址是广东深圳公司街道地址,负责人是刘小姐。

主要经营集成电路。

我们公司主要供应集成电路等产品,我们的产品货真价实,性能可靠,欢迎电话咨询!

本页链接:http://www.cg160.cn/vgy-60467524.html

以上信息由企业自行发布,该企业负责信息内容的完整性、真实性、准确性和合法性。阿德采购网对此不承担任何责任。 马上查看收录情况: 百度 360搜索 搜狗

关于深圳市希罗斯科技有限公司

商铺首页 |

更多产品 |

联系方式

深圳市希罗斯科技有限公司主要经销:ADI TI XILINX ALTERA IDT MSC QORVO CREE Intersil IR等产品。功能涉及:DSP FBGA A/D转换 D/A转换 MCU DDR MOSFET 微波射频等。产品用途涉及:航空航天 ..

- 我要给“XCVU095-2FFVC2104I 数据表”留言

- 更多产品